MIT开发出新芯片 测试堆叠微电子的冷却解决方案

随着对更强大、更高效的微电子系统的需求不断增长,业界正转向3D集成——将芯片堆叠在一起。这种垂直分层架构可以将高性能处理器(例如用于人工智能的处理器)与其他用于通信或成像的高度专业化的芯片紧密封装在一起。但世界各地的技术人员都面临着一个重大挑战:如何防止这些芯片堆叠过热。

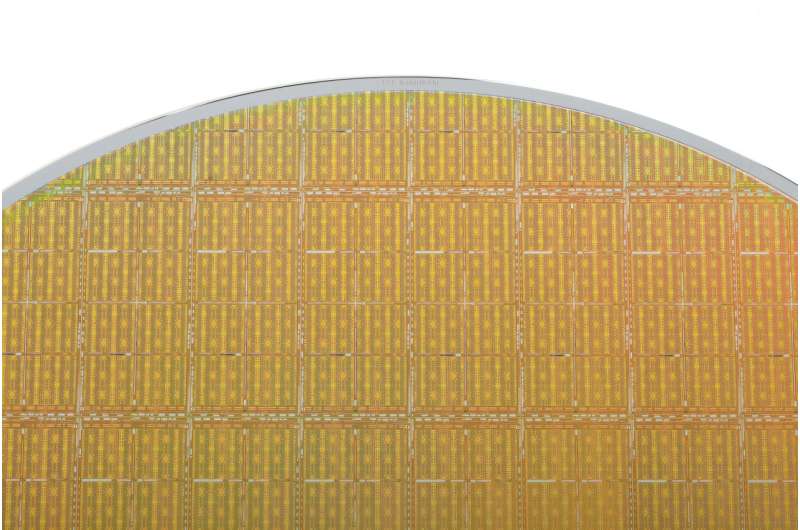

图片来源:MIT

据外媒报道,麻省理工学院(MIT)林肯实验室(Lincoln Laboratory)开发出一种专用芯片,用于测试和验证封装芯片堆叠的冷却解决方案。该芯片功耗极高,模仿高性能逻辑芯片,通过硅层和局部热点产生热量。然后,随着冷却技术应用于封装芯片堆叠,该芯片会测量温度变化。当芯片被夹在芯片堆叠中时,研究人员可以研究热量如何在芯片堆叠层中移动,并评估保持芯片冷却方面的进展。

“如果只有一块芯片,可以从上方或下方进行冷却。但如果将多个芯片堆叠在一起,热量就无处散发。目前还没有任何冷却方法能够让业界堆叠多个如此高性能的芯片,”研究人员Chenson Chen说道。

Chenson Chen与Ryan Keech共同领导了该芯片的开发,两人都来自林肯实验室的先进材料和微系统组。

这款基准芯片目前正由波音(Boeing)和通用汽车(General Motors)共同拥有的研发公司HRL Laboratories使用,用于开发用于3D异质集成(3DHI)系统的冷却系统。异质集成是指将硅芯片与非硅芯片(例如用于射频(RF)系统的III-V族半导体)堆叠在一起。

“射频元件可能会变得非常热,并且运行功率非常高——这给3D集成增加了额外的复杂性,这就是为什么这种测试能力如此重要,”Keech说道。

美国国防高级研究计划局(DARPA)资助了该实验室开发基准测试芯片,以支持HRL项目。所有这些研究都源于DARPA的“用于3D异构集成的微型集成热管理系统”(Minitherms3D)项目。

对于美国国防部而言,3DHI为关键系统开辟了新的机遇。例如,3DHI可以扩大雷达和通信系统的探测范围,使先进传感器能够集成到无人驾驶飞机等小型平台上,或者允许人工智能数据直接在现场系统而非远程数据中心进行处理。

该测试芯片由该实验室微电子实验室的电路设计师、电气测试专家和技术人员共同合作开发。

该芯片具有两个功能:发热和温度传感。为了产生热量,团队设计了能够在极高功率密度下工作的电路,功率密度达到千瓦/平方厘米,与当前及未来高性能芯片的预计功率需求相当。他们还复制了这些芯片中的电路布局,使测试芯片可以作为逼真的替代品。“我们调整了现有的硅技术,本质上是为了设计芯片级加热器,”Chen教授说道。

芯片的加热器模拟了堆栈内的背景热量水平和局部热点。热点通常出现在芯片堆栈最隐蔽、最难以触及的区域,这使得3D芯片开发人员难以评估冷却方案(例如输送冷液的微通道)是否能够到达这些位置并足够有效。

这时,温度传感元件就派上用场了。芯片上分布着一些被陈比作“微型温度计”的元件,它们会在施加冷却液时读取芯片上多个位置的温度。

这些温度计实际上是二极管,或者说是开关,当施加电压时,电流会流过电路。随着二极管升温,电流电压比会发生变化。“我们可以检查二极管的性能,例如知道温度是200°C、100°C还是50°C,”Keech表示。“我们创造性地思考了设备过热失效的原因,然后利用这些特性设计出实用的测量工具。”

Chen和Keech以及实验室的其他设计、制造和电气测试专家目前正在与HRL实验室的研究人员合作,将芯片与新型冷却技术相结合,并将这些技术集成到一个可以增强射频信号功率的3DHI堆栈中。“我们需要冷却相当于190多个笔记本电脑CPU(中央处理器)的热量,但尺寸要与单个CPU封装相同,”HRL联合首席研究员Christopher Roper表示。

Keech表示,芯片交付的快速进度是一项挑战,团队合作克服了芯片设计、制造、测试和3D异构集成等各个阶段的挑战。

声明:本站所有文章资源内容,如无特殊说明或标注,均为采集网络资源。如若本站内容侵犯了原著者的合法权益,可联系本站删除。