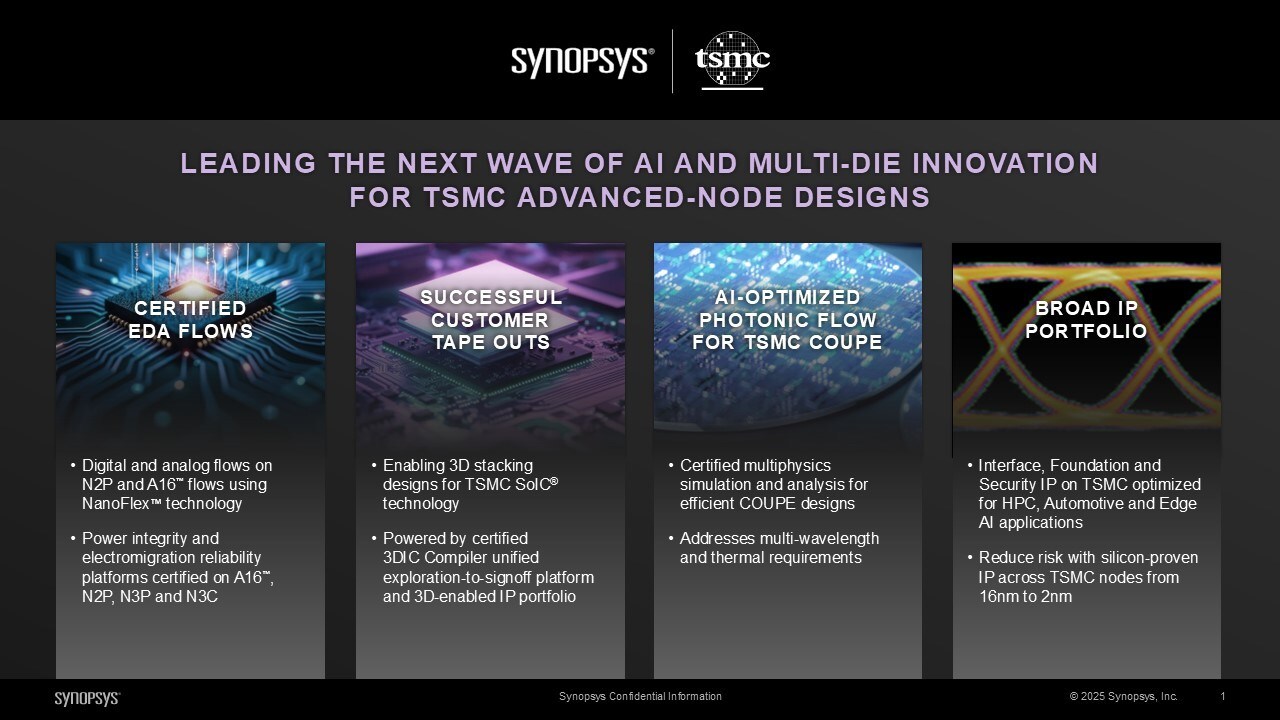

新思科技携手台积电 推动下一波人工智能和多芯片创新浪潮

9月24日,新思科技(Synopsys)宣布与台积电(TSMC)继续合作,提供涵盖先进EDA和IP产品在内的多裸片解决方案,支持台积电领先的工艺和封装技术,推动人工智能(AI)芯片和多裸片设计的创新。

图片来源: 新思科技

3DIC Compiler从探索到签核(exploration-to-signoff)的平台和IP专为3D封装优化,加上新思科技与台积电在设计赋能方面的合作,已促成多个客户流片。

新思科技与台积电持续合作的基础在于提供经过认证的数字和模拟流程,以及采用台积电NanoFlex™架构在台积电N2P和A16™工艺上启用的Synopsys.ai™套件。此外,新思科技还为台积电N5A和N3A工艺提供强大的汽车IP解决方案,以及一流的接口和Foundation IP解决方案,在提供最高级别的安全性、保密性和可靠性的同时,以最低功耗实现先进芯片的最高性能。

新思科技高级副总裁Michael Buehler-Garcia表示:“我们与台积电的密切合作,持续助力工程团队在业界最先进的封装和工艺技术上成功流片。凭借经过认证的数字和模拟EDA流程、3DIC Compiler平台以及针对台积电先进技术优化的全面IP产品组合,新思科技正助力共同客户交付差异化的多裸片和AI设计,从而提升性能、降低功耗并加快上市时间。”

台积电生态系统与联盟管理部总监Aveek Sarkar表示:“台积电一直与新思科技等长期合作的开放创新平台®(OIP)生态系统合作伙伴紧密合作,帮助客户在尖端SoC设计中实现高质量的成果和更快的上市时间。随着对节能和高性能AI芯片的需求日益增长,与OIP生态系统的合作对于为我们的共同客户提供经过认证的EDA工具、流程和高质量IP,以满足甚至超越他们的设计目标至关重要。”

新思科技EDA流程在台积电先进工艺上提供更强大的性能

新思科技的模拟和数字流程以及Synopsys.ai已通过台积电N2P和A16™工艺认证,采用TSMC NanoFlex™架构,有助于优化性能和功耗,并将芯片设计扩展到先进的半导体技术。TSMC A16™超级电源轨(SPR)工艺上的认证功能可改善电源分配和系统性能,同时保持背面布线设计的热稳定性。新思科技基于模式的引脚访问方法已针对TSMC A16™节点进行了增强,以提供具有竞争力的面积优化结果。此外,新思科技正与台积电合作开发针对台积电A14工艺的设计流程,并计划于2025年下半年发布首个工艺设计套件。

Synopsys IC Validator™ signoff物理验证解决方案已通过台积电A16™工艺认证,支持DRC和LVS检查。 IC Validator的高容量弹性架构无缝扩展PERC规则,以处理台积电的N2P全路径静电放电(ESD)验证,并缩短周转时间。

先进的3D堆叠和CoWoS技术展现成功的3D集成

新思科技3DIC Compiler的统一探索到签核平台已启用,支持TSMC-SoIC®(SoIC-X)技术,包括3D堆叠设计以及采用CoWoS®技术的硅中介层和桥接器,并已帮助客户完成多项流片。借助3DIC Compiler,客户可以通过该平台的自动化UCIe和HBM布线、TSV和凸块规划以及多芯片签核验证,实现更高的生产效率和更快的周转时间。

此外,新思科技与台积电在硅光子学领域的持续合作,为TSMC-COUPE™技术打造了经过AI优化的光子集成电路流程,从而提升系统性能,并满足多芯片和AI设计中的多波长和散热要求。

声明:本站所有文章资源内容,如无特殊说明或标注,均为采集网络资源。如若本站内容侵犯了原著者的合法权益,可联系本站删除。